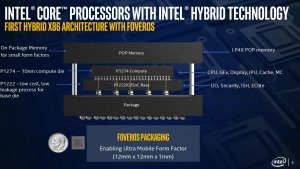

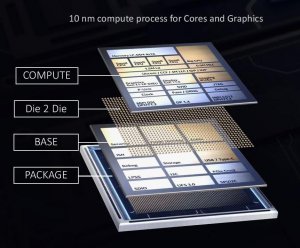

Intel's Rube Goldberg Atom-Core Hybrid with multiple Layers, that performs like an Atom.

It looks like a lot more complexity (and thus cost) for a questionable benefit.

https://www.anandtech.com/show/15877/intel-hybrid-cpu-lakefield-all-you-need-to-know

It looks like a lot more complexity (and thus cost) for a questionable benefit.

https://www.anandtech.com/show/15877/intel-hybrid-cpu-lakefield-all-you-need-to-know

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)